XXIII SNPTEE SEMINÁRIO NACIONAL DE PRODUÇÃO E TRANSMISSÃO DE ENERGIA ELÉTRICA

FI/GDS/11 18 a 21de Outubro de 2015 Foz do Iguaçu - PR

**GRUPO - X**

# GRUPO DE ESTUDO DE DESEMPENHO DE SISTEMAS ELÉTRICOS - GDS

# SISTEMA DE SINCRONIZAÇÃO BASEADO EM PLL (PHASE-LOCKED LOOP) MONOFÁSICO E TRIFÁSICO COM IMUNIDADE A DISTÚRBIOS

Renato Guerreiro Araújo\* UNIVERSIDADE FEDERAL DO CEARÁ Francisco Kleber de A. Lima UNIVERSIDADE FEDERAL DO CEARÁ

Carlos Gustavo C. Branco UNIVERSIDADE FEDERAL DO CEARÁ

## **RESUMO**

O presente trabalho apresenta um novo algoritmo de sincronização PLL (Phase-Locked Loop) para aplicações na área de sistemas de controle de conversores de potência no que diz respeito ao condicionamento de energia em redes monofásicas e trifásicas. A estrutura apresentada tem como base a correlação do sinal de entrada com um sinal complexo gerado a partir de um filtro adaptativo em um algoritmo PLL, a fim de minimizar o seu custo computacional e aumentar o nível de rejeição a inter harmônicos e sub harmônicos, quando comparado ao algoritmo original. Serão apresentados simulações e resultados experimentais visando comprovar a eficácia deste algoritmo adaptado.

## PALAVRAS-CHAVE

Phase-Locked Loop, Sincronização, Filtro Adaptativo, Conversores de Potência.

## 1.0 - INTRODUÇÃO

Em aplicações relacionadas com conversores de potência, o método de sincronização representa um elemento chave no desempenho da estratégia de controle destes equipamentos. Quando o sinal de entrada caracteriza-se como uma senóide pura, um detector de passagem por zero realiza esta tarefa de forma satisfatória. Contudo, diante da existência de harmônicos no sinal de entrada, esta metodologia de detecção e outros métodos procedentes deste, não proporcionam, em geral, resultados satisfatórios [1-2].

Diferentes algoritmos foram apresentados no sentido de detectar o ângulo de fase, a frequência e a magnitude da componente fundamental da tensão de entrada [3-7]. Porém, estes algoritmos não apresentam um bom desempenho quando esta forma de onda apresenta distorções devido a presença de harmônicos. Além disto, como a detecção ocorre a cada meio ciclo do sinal de entrada, a resposta dinâmica é lenta [8]. Os valores estimados com os algoritmos indicam que, diante de sinais fortemente distorcidos, faz-se necessário reajustar os parâmetros destes métodos obtendo uma resposta mais lenta, caso contrário, a saída estimada será afetada acentuadamente.

Além destes fatos, a presença (em particular) de sub e inter harmônicos em sistemas elétricos causam oscilações sub síncronas em sistemas mecânicos, *flickers*, sobreaquecimento, redução da vida útil e mau funcionamento de equipamentos. Salienta-se que com a difusão da utilização de unidades de geração distribuídas baseadas em conversores de potência nas redes de distribuição, a importância dos métodos confiáveis de sincronização fica ainda mais acentuada [9-10].

Diante do exposto, esse artigo dedica-se a apresentar dois algoritmos PLL, um monofásico e outro trifásico, que apresentam alta capacidade de rejeição a inter harmônicos e sub harmônicos com reduzido esforço computacional. Os algoritmos propostos baseiam-se em filtro adaptativo que proporciona redução no número de operações matemáticas e melhoria na rejeição a distúrbios. A partir da estrutura do PLL monofásico, com as devidas alterações, pode-se obter a estrutura trifásica.

Sistemas de sincronização baseados nos algoritmos monofásicos e trifásicos propostos são avaliados neste trabalho por meio de análises matemáticas e simulações computacionais realizadas através do software PSCAD/EMTDC. Por fim, serão apresentados resultados experimentais obtidos através de plataforma HIL (*Hardware-in-the-Loop*), os quais serão comparados aos obtidos em simulação visando validar o estudo proposto.

## 2.0 - ALGORITMO DO PLL COM IMUNIDADE A DISTORÇÕES HARMÔNICAS

## 2.1 Estrutura Monofásica

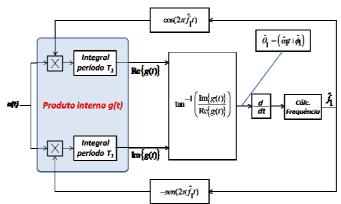

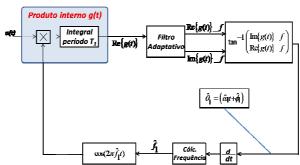

A estrutura do PLL monofásico proposto em [11] está representada na Figura 1. Esta estrutura possibilita estimar frequência  $\overline{f_1}$ , o ângulo de sincronismo  $\overline{f_1}$  (1) e a componente fundamental do sinal de entrada u(t).

FIGURA 1 - Estrutura do PLL monofásico.

Com a correta estimação da frequência  $\mathbf{f_1} = \mathbf{f_1}$  da componente fundamental do sinal de entrada  $\mathbf{u(t)}$ , o ângulo de fase da componente fundamental deste sinal  $\mathbf{f_1} = \mathbf{f_1}$  poderá ser determinada por meio da projeção de  $\mathbf{u(t)}$  no subespaço complexo  $\mathbf{e^{-j2\pi f_1 t}}$  durante um ciclo do sinal de entrada. Assim, têm-se representado um produto interno  $\mathbf{g(t)}$  que garante uma correlação apenas entre os sinais ortogonais do subespaço na frequência fundamental e a componente fundamental do sinal de entrada.

O produto interno **g(t)** é uma função complexa composta por uma parte real **Re{g(t)}** e outra parte imaginária **Im{g(t)}**, sendo representado por:

$$g(t) = \int u(t)e^{-j(2\pi\hat{f}_1t)}dt = \text{Re}\{g(t)\} + j\text{Im}\{g(t)\}$$

(1)

A parte real e imaginária de (1) representam correlatores entre o sinal de entrada  $\mathbf{u}^{(t)}$  e a exponencial complexa  $\mathbf{e}^{-j2\pi \mathbf{f}_1 \mathbf{t}}$ . Sendo assim, os sinais ortogonais  $\mathbf{Re}(\mathbf{g}(\mathbf{t}))$  e  $\mathbf{Im}(\mathbf{g}(\mathbf{t}))$  oriundos de (1), serão sempre diferentes de zero apenas na frequência fundamental do sinal de entrada  $\mathbf{u}^{(t)}$  garantindo uma imunidade a interferência por harmônicos.

A partir do exposto, sendo u(t):

$$u(t) = Asen(2\pi ft + \phi) + Harmoni \cos$$

(2)

Considera-se apenas a componente fundamental do sinal de entrada, devido ao cálculo do produto interno. Com isso, tem-se que a parte real da função complexa definida em (1) para a frequência fundamental é:

$$\operatorname{Re}\left\{g(t)\right\} = \frac{Ae^{-j(2\pi\hat{f}_{1}t)}}{2\pi(\hat{f}_{1}^{2} - f^{2})} f \cos(2\pi f t + \phi) \tag{3}$$

Já a parte imaginária da função complexa definida em (1) para a frequência fundamental é:

$$\operatorname{Im}\{g(t)\} = \frac{Ae^{-j(2\pi\hat{f}_{1}t)}}{2\pi(\hat{f}_{1}^{2} - f^{2})} \hat{f}_{1}sen(2\pi ft + \phi)$$

(4)

Utilizando os sinais ortogonais **Re{g(t)}** e **Im{g(t)}**, pode-se determinar o ângulo de sincronismo da componente fundamental do sinal de entrada **u(t)** por:

$$\hat{\theta}_{l}(t) = \tan^{-1} \left( \frac{\operatorname{Im} \{ g(t) \}}{\operatorname{Re} \{ g(t) \}} \right) = \left( 2\pi \hat{f}_{l} t + \phi_{l} \right) \tag{5}$$

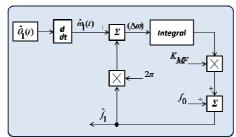

A partir da informação do ângulo de sincronismo  $\hat{\theta}_1$ , é obtida a frequência angular  $\hat{\omega}_1$  derivando-se  $\hat{\theta}_1$ . A frequência angular  $\hat{\omega}_1$ é a entrada da malha interna que realiza o cálculo da frequência fundamental em Hz do sinal de entrada. A malha interna que realiza o cálculo da frequência está ilustrada na Figura 2.

FIGURA 2 - Malha interna de estimação de frequência.

Adotando  $\mathbf{f}_0$  como uma estimativa inicial da frequência em Hz, a frequência estimada  $\mathbf{f}_1$  em qualquer instante de tempo será:

$$\hat{f}_1(t) = \int \left(\frac{1}{2\pi dt}\hat{\theta}_1(t) - \hat{f}_1\right)dt + f_0 \tag{6}$$

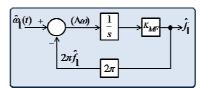

Analisando o diagrama de blocos exposto na Figura 2 no domínio da frequência, tem-se que a malha interna de estimação da frequência realiza ainda o papel de um filtro passa baixa com a função de transferência dada por (7) e representada pelo diagrama de blocos da Figura 3. Ressalta-se que a saída da integral de  $\Delta\omega$  em rad/s é multiplicada por um ganho em 1/rad, resultando na adequação da unidade da freqüência estimada  $f_1$  em Hz.

$$\frac{\hat{f}_{1}(s)}{\hat{c}_{1}(s)} = \frac{K_{MF}}{s + 2\pi K_{MF}} \tag{7}$$

FIGURA 3 – Diagrama de blocos da malha interna de estimação de frequência.

## 2.2 Estrutura Trifásica

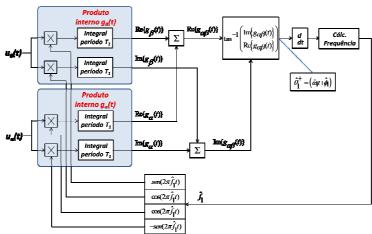

Alguns modelos de estruturas de sincronismo monofásicas servem como base para a determinação de modelos trifásicos. A partir da estrutura monofásica apresentada no Tópico 2.1, obtém-se, como é apresentado em [12], a estrutura do PLL trifásico.

A estrutura do PLL trifásico proposto em [12] está representada na Figura 4. Esta estrutura possibilita estimar a frequência  $\overline{f_1}$ , o ângulo de sincronismo de sequência positiva  $\overline{\theta_1}(t)$  e a componente fundamental de sequência positiva do sinal de entrada.

$$u_{3\phi}(t) = \begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix} = \begin{bmatrix} Asen(2\pi f_1 t + \phi_1) \\ Asen(2\pi f_1 t + \phi_1 - 2\pi/3) \\ Asen(2\pi f_1 t + \phi_1 - 4\pi/3) \end{bmatrix}$$

(8)

Tem-se que os mesmos podem ser representados em coordenadas  $\alpha\beta$  por:

$$u_{\alpha\beta}(t) = \begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = \begin{bmatrix} Asen(2\pi f_{1}t + \phi_{1}) \\ Asen(2\pi f_{1}t + \phi_{1} - \frac{\pi}{2}) \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3}/2 & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} u_{\alpha} \\ u_{\beta} \\ u_{\alpha} \end{bmatrix}$$

(9)

FIGURA 4 - Estrutura do PLL trifásico.

A correta estimação da frequência deste conjunto de sinais, possibilita a obtenção de um subespaço complexo o qual pode ser representado pelas exponenciais em coordenadas αβ, respectivamente, por:

$$\begin{cases} e^{-j(2\pi\hat{f}_{i}t)} \\ e^{-j(2\pi\hat{f}_{i}t-\pi/2)} \end{cases}$$

(10)

Utilizando a modelagem do sistema em coordenadas  $\alpha\beta$ , tem-se que o produto interno  $\mathbf{g}_{\alpha\beta}(\mathbf{t})$  pode ser calculado a partir de (9) e (10). O produto interno  $\mathbf{g}_{\alpha\beta}(\mathbf{t})$  é composto por uma parcela na coordenada  $\alpha$  e outra na coordenada  $\beta$ . Este produto é representado por:

$$g_{\alpha\beta}(t) = \begin{bmatrix} g_{\alpha}(t) \\ g_{\beta}(t) \end{bmatrix} = \begin{bmatrix} \int u_{\alpha}(t)e^{-j(2\pi\hat{f}_{\parallel}t)} \\ \int u_{\beta}(t)e^{-j(2\pi\hat{f}_{\parallel}t - \frac{\pi}{2})} \end{bmatrix} = \begin{bmatrix} \operatorname{Re}\{g_{\alpha}(t)\} + \operatorname{Im}\{g_{\alpha}(t)\} \\ \operatorname{Re}\{g_{\beta}(t)\} + \operatorname{Im}\{g_{\beta}(t)\} \end{bmatrix}$$

$$(11)$$

Cada produto interno gera um sinal real e outro imaginário, a partir dos quais pode-se calcular o sinal real e imaginário equivalente do sinal de entrada. Calculando-se esse produto interno, tem-se que as partes reais e imaginárias equivalentes são:

$$\begin{bmatrix}

\operatorname{Re}\left\{g_{\alpha\beta}(t)\right\} \\

\operatorname{Im}\left\{g_{\alpha\beta}(t)\right\}

\end{bmatrix} = \begin{bmatrix}

\operatorname{Re}\left\{g_{\alpha}(t)\right\} + \operatorname{Re}\left\{g_{\beta}(t)\right\} \\

\operatorname{Im}\left\{g_{\alpha}(t)\right\} + \operatorname{Im}\left\{g_{\beta}(t)\right\}

\end{bmatrix}$$

(12)

Utilizando os sinais real  $\mathbb{R}^{\mathbf{e}}[g]_{\alpha\beta}(t)$  e imaginário  $\mathbb{E}^{\mathbf{m}}[g]_{\alpha\beta}(t)$  resultantes de (12), determina-se o ângulo de sincronismo da componente de sequência positiva do sinal de entrada.

$$\hat{\theta}_{l}^{+} = \tan^{-1} \left( \frac{\operatorname{Im} \left\{ g_{\alpha\beta}(t) \right\}}{\operatorname{Re} \left\{ g_{\alpha\beta}(t) \right\}} \right) = \left( 2\pi \hat{f}_{l} t + \hat{\phi}_{l} \right) \tag{13}$$

A partir do exposto, com a informação do ângulo de sincronismo  $\bar{\theta}_1$ , pode-se obter a frequência fundamental do sinal de entrada adotando-se as mesmas premissas para o cálculo da frequência do Tópico 2.1.

## 3.0 - ALGORITMO DO PLL OTIMIZADO

## 3.1 Estrutura Monofásica

Fazendo modificações na estrutura proposta por [11], considerou-se somente o processo de cálculo da parte real  $\mathbf{Reg(t)}$  do produto interno  $\mathbf{g(t)}$  dado pela expressão (3). A parte imaginária  $\mathbf{Im}\{\mathbf{g(t)}\}$ , é estimada por meio de um filtro adaptativo em que a entrada é o sinal  $\mathbf{Re}\{\mathbf{g(t)}\}$ . Utilizando-se o filtro adaptativo, têm-se a obtenção de dois sinais ortogonais  $\mathbf{Re}\{\mathbf{g(t)}\}_{\mathbf{f}}$  e  $\mathbf{Im}\{\mathbf{g(t)}\}_{\mathbf{f}}$  a partir da entrada  $\mathbf{Re}\{\mathbf{g(t)}\}$ . Isso faz com que o número de operações matemáticas sejam reduzidas e que haja um aumento na rejeição a harmônicos. O restante do algoritmo é o mesmo do algoritmo original. A Figura 5 ilustra o diagrama de blocos do PLL considerando a inserção do filtro adaptativo.

FIGURA 5 – Estrutura do PLL monofásico otimizado.

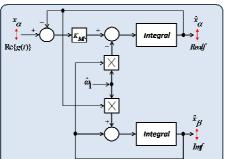

O filtro adaptativo, apresentado na Figura 6, foi obtido a partir de um modelo para sistemas trifásicos analisado em [13].

FIGURA 6 - Diagrama de blocos do filtro adaptativo.

O filtro adaptativo apresenta as seguintes expressões resultantes:

$$\frac{\hat{x}_{\alpha}(s)}{x_{\alpha}(s)} = \frac{K_{MF}(s+1)}{s^2 + s(K_{MF}+1) + K_{MF} + \hat{\alpha}_1^2}$$

(14)

$$\frac{\hat{x}\beta(s)}{x_{\alpha}(s)} = \frac{K_{MF}\hat{\alpha}_{l}}{s^{2} + s(K_{MF} + l) + K_{MF} + \hat{\alpha}_{l}^{2}}$$

$$\tag{15}$$

Com a utilização do filtro adaptativo, os sinais real e imaginário estarão menos afetados pelos distúrbios em relação sinal de entrada **Re{g(t)}**.

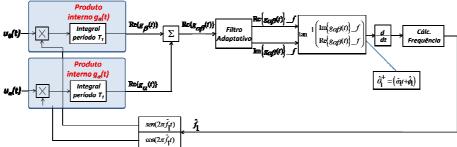

## 3.2 Estrutura Trifásica

Fazendo modificações na estrutura proposta por [12], considerou-se somente o processo de cálculo da parte real  $\mathbf{Re}\{\mathbf{g}_{\alpha\beta}(t)\}$  do produto interno  $\mathbf{g}_{\alpha\beta}(t)$  dado pela expressão (12). A parte imaginária  $\mathbf{Im}\{\mathbf{g}_{\alpha\beta}(t)\}$ , é estimada por meio de um filtro adaptativo em que a entrada é o sinal  $\mathbf{Re}\{\mathbf{g}_{\alpha\beta}(t)\}$ . Sendo assim, têm-se a obtenção de dois

sinais ortogonais  $\operatorname{Re}\left[g_{\alpha\beta}(t)\right]_f = \operatorname{Im}\left[g_{\alpha\beta}(t)\right]_{f'}$  a partir da entrada  $\operatorname{Re}\left[g_{\alpha\beta}(t)\right]$ . Isso faz com que o número de operações matemáticas sejam reduzidas e que haja um aumento na rejeição a harmônicos. O restante do algoritmo é o mesmo do algoritmo original. A Figura 7 ilustra o diagrama de blocos do PLL considerando a inserção do filtro adaptativo.

FIGURA 7 - Estrutura do PLL trifásico otimizado.

Com a utilização do filtro adaptativo, os sinais real e imaginário estarão menos afetados pelos distúrbios em relação sinal de entrada Re{gaß(t)}.

# 4.0 - RESULTADOS DE SIMULAÇÃO

## 4.1 Estrutura Monofásica

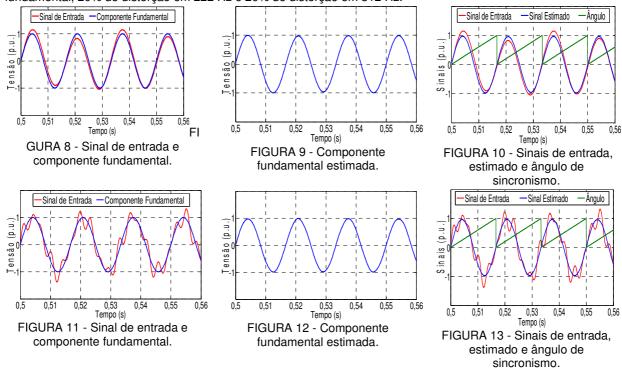

A fim de validar o estudo, realizaram-se simulações no software PSCAD/EMTDC. Simulou-se dois cenários, o primeiro com a presença de sub harmônico e o segundo com a presença de inter harmônico. No primeiro cenário (Figuras 8 a 10) a tensão de entrada é composta pela componente fundamental, 10% de distorção em 30 Hz e 10% de distorção em 36 Hz. No segundo cenário (Figuras 11 a 13) a tensão de entrada é composta pela componente fundamental, 20% de distorção em 222 Hz e 20% de distorção em 312 Hz.

### 4.2 Estrutura Trifásica

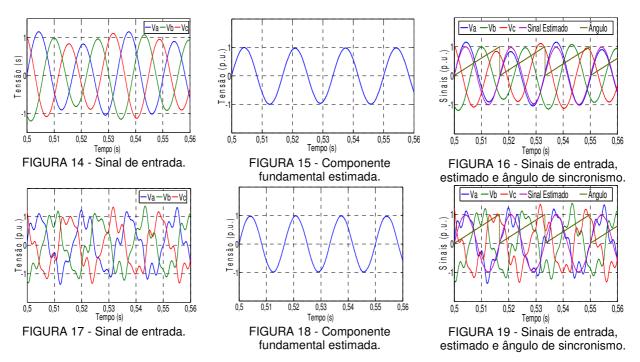

Assim como na estrutura monofásica, simulou-se dois cenários no software PSCAD/EMTDC. No primeiro cenário (Figuras 14 a 16) a tensão de entrada é composta pela componente fundamental, 10% de distorção em 30 Hz e 10% de distorção em 36 Hz. No segundo cenário (Figuras 17 a 19) a tensão de entrada é composta pela componente fundamental, 20% de distorção em 222 Hz e 20% de distorção em 312 Hz.

A próxima seção apresenta os resultados experimentais implementados a partir da plataforma HIL (*Hardware-in-the-Loop*) DSPACE 1103.

## 5.0 - RESULTADOS EXPERIMENTAIS

## 5.1 Estrutura Monofásica

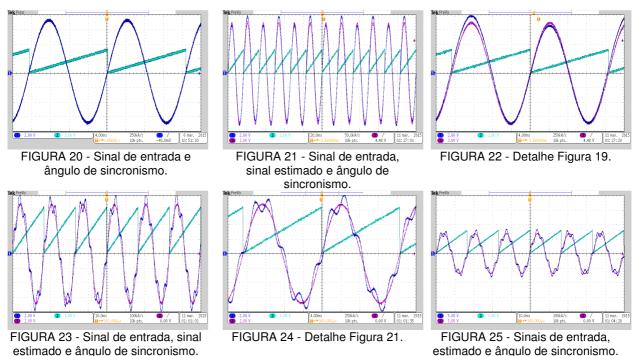

A Figura 20 apresenta o ângulo de sincronismo para um sinal de entrada senoidal com frequência de 60 Hz. As Figuras 21 e 22 apresentam o ângulo de sincronismo e o sinal estimado para um sinal de entrada composto pela componente fundamental e 10% de sub harmônico em 30 Hz. As Figuras 23 a 25 apresentam o ângulo de sincronismo e o sinal estimado para um sinal de entrada composto pela componente fundamental e 20% de inter harmônico em 312 Hz.

#### 5.2 Estrutura Trifásica

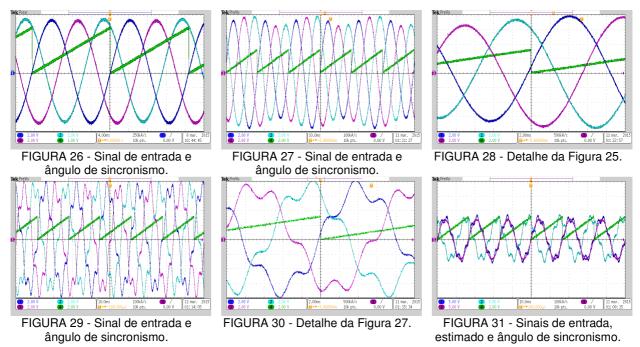

A Figura 26 apresenta o ângulo de sincronismo para um sinal de entrada senoidal com frequência de 60 Hz. As Figuras 27 e 28 apresentam o ângulo de sincronismo e o sinal estimado para um sinal de entrada composto pela componente fundamental e 10% de sub harmônico em 30 Hz. As Figuras 29 a 31 apresentam o ângulo de sincronismo e o sinal estimado para um sinal de entrada composto pela componente fundamental e 20% de inter harmônico em 312 Hz

## 6.0 - CONCLUSÃO

Neste trabalho foi apresentado um novo algoritmo de PLL (*Phase-Locked Loop*) o qual pode ser usado tanto em sistemas de sincronização trifásicos quanto monofásicos. A presença de sub e inter harmônicos afeta os valores estimados de determinados sistemas de sincronização. Uma das principais características deste PLL é a alta imunidade a sub e inter harmônicos. A fim de se comprovar a eficácia dos algoritmos apresentados, fez-se simulações através do software PSCAD/EMTDC e foram montadas duas estruturas do PLL em plataforma HIL (*Hardware-in-the-Loop*). As estruturas foram submetidas a um sinal de entrada composto somente pela componente fundamental em 60 Hz, e além disto, em particular, submeteu-se as estruturas a sinais com a presença de distorções, como inter harmônicos e sub harmônicos. Devido à robustez do modelo proposto, os algoritmos apresentaram boas respostas, as quais não foram afetadas pelo nível de distorção harmônica no sinal de entrada. Em particular, o algoritmo apresentou bons resultados, comprovando a sua capacidade de rejeição a inter harmônicos e sub harmônicos. Nesse contexto, o algoritmo possibilita uma detecção precisa mesmo diante de elevados níveis de distorção.

Os resultados obtidos deixaram claro que estes algoritmos são capazes de estimar o ângulo de sincronismo, a frequência e a componente fundamental do sinal de entrada, com isso eles podem ser implementados e utilizados em estratégias de controle de equipamentos baseados em eletrônica de potência.

## 7.0 - REFERÊNCIAS BIBLIOGRÁFICAS

- (1) Väliviita, S. "Zero-Crossing Detection of Distorted Line Voltages Using 1-b Measurements", IEEE Transactions on Industrial Electronics, vol. 46, no. 5, pp. 917-922, 1999.

- (2) Lee, K.-J., Lee, J.-P., Shin, D., Yoo, D.-W., Kim, H.-J. "A Novel Grid Synchronization PLL Method Based on Adaptive Low-Pass Notch Filter for Grid-Connected PCS", IEEE Transactions on Industiral Electronics, vol. 61, no. 1, pp. 292-301, 2014.

- (3) Ghartemani, M. K., Karime, H., Iravani, M. R. "A Magnitude/Phase-Locked Loop System Based on Estimation of Frequency and In-Phase/Quadrature-Phase Amplitudes", IEEE Transactions on Industrial Electronics, vol. 51, no. 2, pp. 511-517, April, 2004.

- (4) Pádua, M. S., Deckmann, P. M., Lopes, A., Marafão, F. "Metodologia para Identificação do Componente Fundamental da Tensão da Rede Baseada no Algoritmo Recursivo da TDF", Revista Controle & Automação, vol. 18, no. 3, pp. 381-395.

- (5) Silva, S. A. O., Novochadlo, R., Modesto, R. A. "Single-phase PLL Structure Using Modified p-q Theory for Utility Connected Systems", in 39th IEEE Power Electronics Specialists Conference (PESC), 2008, pp. 4706-4711.

- (6) Thacker, T., Wang, R., Dong, D., Burgos, R., Wang, F., Boroyevich, D. "Phase Locked Loop Using State Variable Feedback for Single-Phase Converter Systems", in 24th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2009, pp. 864-870.

- (7) Wang, Z., Wang, Y., Wu, S. "Enhanced Single-phase Locked Loop for Grid-Connected Converter in Distribution Network", in IEEE International Conference on Electrical and Control Engineering (ICECE), 2010, pp. 3705-3709.

- (8) Thacker, T., Boroyevich, D., Burgos, R., Wang, F. "Phase-Locked Loop Noise Reduction via Phase Detector Implementation for Single-Phase Systems", IEEE Transactions on Industrial Electronics, vol. 58, no. 6, pp. 2482-2490, 2011.

- (9) Blaabjerb, F., Teodorescu, R., Lissere, M., Timbus, A. V. "Overview of Control and Grid Synchronization for Distributed Power Generation Systems", IEEE Transactions on Industrial Electronics, vol. 53, no. 5, pp. 1398-1409, 2006.

- (10) Testa, A., Akram, M. F., Burch, R., Carpinelli, G., Chang, G., Dinavahi, V., Hatziadoniu, C., Grady, W. M., Gunther, E., Halpin, M., Lehn, P., Liu, Y., Langella, R., Lowenstein, M., Medina, A., Ortmeyer, T., Ranade, S., Ribeiro, P., Watson, N., Wikston, J., Xu, W. "Interharmonics: Theory and Modeling", IEEE Transactions on Power Delivery, vol. 22, no. 4, pp. 2335-2348, 2007.

- (11) Lovisolo, L., Neto, J. A. M., Ferreira, J. C., Aredes, M. "Implementação Digital de um Algoritmo PLL (Phase-Locked Loop) com Alta Imunidade às Distorções Harmônicas", VIII Conferência Internacional de Aplicações Industriais (Induscon), Poços de Caldas, 2008.

- (12) Neto, J. A. M. "Contribuições para o Desenvolvimento do Condicionador Unificado de Energia (*UPQC Unified Power QualityConditioner*).2008. 246 f. Tese (Doutorado em Engenharia Elétrica) Programa de Pós Graduação em Engenharia, Universidade Federal do Rio de Janeiro, Rio de Janeiro, 2008.

- (13) Benhabib, M. C., Saadate, S."A New Topology for a Modular Active Power Filter", IEEE International Symposium on Industrial Electronics (ISIE), 2005, pp. 827-832.

## 8.0 - DADOS BIOGRÁFICOS

Renato Guerreiro Araújo, nascido em 16 de maio de 1990 em Maranguape é Engenheiro Eletricista (2013), pela Universidade Federal do Ceará. Atualmente cursa mestrado através do Programa de Pós Graduação em Engenharia Elétrica da Universidade Federal do Ceará. Suas áreas de interesse são: Eletrônica de Potência, Qualidade de Energia e Sistemas de Sincronização.

Francisco Kleber de A. Lima, nascido em 03 de novembro de 1968 em Fortaleza é Engenheiro Eletricista (1998) e Mestre em Engenharia Elétrica (2003), pela Universidade Federal do Ceará. Recebeu o título de Doutor em Engenharia Elétrica pela COPPE/Universidade Federal do Rio de Janeiro em 2009. Dr. Kleber Lima é professor do Departamento de Engenharia Elétrica da Universidade Federal do Ceará. Suas áreas de interesse são: Eletrônica de Potência, Qualidade de Energia e Acionamentos de Máquinas Elétricas. Francisco Kleber de A. Lima é membro da SOBRAEP desde 2002.

Carlos Gustavo Castelo Branco, possui Graduação em Engenharia Elétrica pela Universidade Federal do Ceará (2002) e mestrado em Engenharia Elétrica pela Universidade Federal do Ceará (2005). Durante o Mestrado trabalhou em Projetos de P&D na área de Fontes Ininterruptas de Energia(UPS) e Conversores de Alta Potência. Desde 2005 trabalha na área de Pesquisa e Desenvolvimento de sistemas UPS Isolados em Alta Frequência, Sistemas de Energia Fotovoltaica e Acionamentos de Máquinas. Atualmente é professor assistente do Departamento de Engenharia Elétrica da Universidade Federal do Ceará. É membro do IEEE e SOBRAEP.